# SESDM5V0T143

# SUMSEMI

# 2-Line Ultra-Low Capacitance TVS Diode Array

#### Description

The SESDM5V0T143 is a 2-line ultra-low capacitance TVS diode array, to provide fast response time and low ESD clamping voltage, making this device an ideal solution for protecting voltage sensitive high-speed data lines. The SESDM5V0T143 has a very low capacitance with a typical value at 0.4pF, and complies with the IEC 61000-4-2 (ESD) with ±15Kv air and ±8kV contact discharge. It is assembled into a 4-pin SOT-143 lead-free package. The small size, very low capacitance and high ESD protection make SESDM5V0T143 an ideal choice to protect cell phone, digital video interfaces, high speed data ports, and many other portable applications.

#### Features

- Ultra low capacitance: 0.4pF typical

- Ultra low leakage: nA level

- Operating voltage: 5V

- Low clamping voltage

- 4-pin SOT-143 package

- Protects two data lines and one power line

- Complies with following standards:

- IEC 61000-4-2 (ESD) immunity test

Air discharge: ±15kV

Contact discharge: ±8kV

- IEC61000-4-5 (Lightning) 6.5A (8/20µs)

- RoHS Compliant

#### **Ordering Information**

| Part Number  | Shipping         | Reel Size |  |

|--------------|------------------|-----------|--|

| SESDM5V0T143 | 3000/Tape & Reel | 7 inch    |  |

#### **Mechanical Characteristics**

- Package: SOT-143

- Lead Finish: Matte Tin

- Case Material: "Green" Molding Compound

- Moisture Sensitivity: Level 3 per J-STD-020

#### Applications

- FireWire & USB

- Sensitive Analog Inputs

- Portable Electronics

- LAN/WAN equipment

- Video Line Protection

- Microcontroller Input Protection

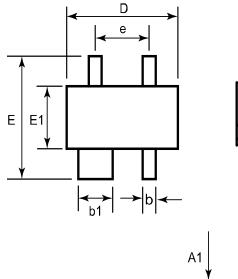

#### **Dimensions and Pin Configuration**

Circuit Diagram

Pin Schematic

# Absolute Maximum Ratings ( $T_A$ =25°C unless otherwise specified)

| Parameter                       | Symbol          | Value       | Unit |

|---------------------------------|-----------------|-------------|------|

| Peak Pulse Power (8/20µs)       | P <sub>PK</sub> | 100         | W    |

| Peak Pulse Current (8/20µs)     | I <sub>PP</sub> | 6.5         | A    |

| ESD per IEC 61000-4-2 (Air)     | V               | ±15         |      |

| ESD per IEC 61000-4-2 (Contact) | $V_{ESD}$       | ±8          | kV   |

| Operating Temperature Range     | T <sub>OP</sub> | -55 to +125 | C    |

| Storage Temperature Range       | Tstg            | −55 to +150 | С    |

# Electrical Characteristics ( $T_{\underline{A}}$ =25°C unless otherwise specified)

| Parameter               | Symbol           | Min | Тур | Max  | Unit | Test Condition                                                   |

|-------------------------|------------------|-----|-----|------|------|------------------------------------------------------------------|

| Reverse Working Voltage | V <sub>RWM</sub> |     |     | 5    | V    | Any I/O pin to ground                                            |

| Breakdown Voltage       | V <sub>BR</sub>  | 6   |     |      | V    | I <sub>T</sub> = 1mA, any I/O pin to ground                      |

| Reverse Leakage Current | I <sub>R</sub>   |     |     | 20   | nA   | V <sub>RWM</sub> = 5V, any I/O pin to ground                     |

| Clamping Voltage        | Vc               |     |     | 10   | V    | I <sub>PP</sub> = 1A (8 x 20µs pulse), any I/O<br>pin to ground  |

| Clamping Voltage        | Vc               |     | 16  | 17.6 | V    | I <sub>PP</sub> =6.5A (8 x 20µs pulse), any<br>I/O pin to ground |

| Junction Capacitance    | CJ               |     | 0.8 | 1.0  | pF   | V <sub>R</sub> = 0V, f = 1MHz, between I/O<br>pins               |

| Junction Capacitance    | CJ               |     | 0.4 | 0.6  | pF   | V <sub>R</sub> = 0V, f = 1MHz, any I/O pin to ground             |

Note 1: I/O pins are pin 2 & 3

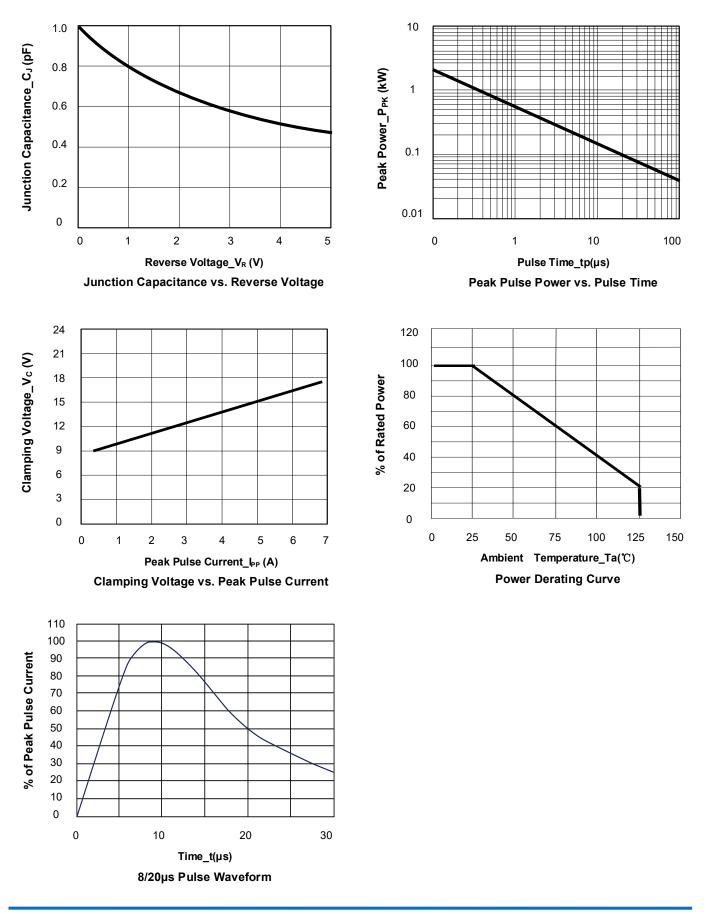

## Typical Performance Characteristics (T<sub>A</sub>=25°C unless otherwise Specified)

3

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. **SUMSEMI** (and designs) are registered trademarks of SUM Semiconductor Corporation. Copyright SUM Semiconductor Corporation. All Rights Reserved. All other trademarks mentioned are the property of their respective owners.

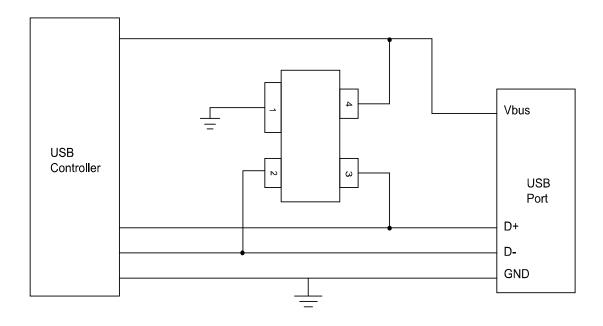

#### SESDM5V0T143 on USB Port Application

The SESDM5V0T143 can be used to protect the USB port on the monitors, computers, peripherals or portable systems. The ESD protection scheme for single USB ports is shown below figure, the voltage bus ( $V_{BUS}$ ) of USB port is connected to the power pin (pin4) of SESDM5V0T143. Each data line (D+/D-) of USB port is connected to the ESD protection pin (pin2/pin3) of SESDM5V0T143. When ESD voltage pulse appears on the data line, the ESD pulse current will be conducted by SESDM5V0T143 away from the USB controller chip. In addition, the ESD pulse current also can be conducted by SESDM5V0T143 away from the USB controller chip when the ESD voltage pulse appears on the voltage bus (VBUS) of USB port. Therefore, the data lines (D+/D-) and voltage bus (V<sub>BUS</sub>) of two USB ports are complementally protected with one SESDM5V0T143.

DIMENSIONS

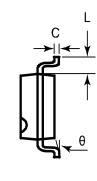

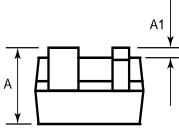

## SOT-143 Package Outline Drawing

| SYM | MILLIMETERS |          | INCHES   |       |          |       |

|-----|-------------|----------|----------|-------|----------|-------|

|     | MIN         | NOM      | MAX      | MIN   | NOM      | МАХ   |

| А   | 0.80        |          | 1.22     | 0.031 |          | 0.048 |

| A1  | 0.013       |          | 0.15     | 0.00  |          | 0.006 |

| b   | 0.30        |          | 0.51     | 0.011 |          | 0.020 |

| b1  | 0.76        |          | 0.94     | 0.029 |          | 0.037 |

| С   | 0.08        |          | 0.20     | 0.003 |          | 0.008 |

| D   | 2.80        | 2.90     | 3.04     | 0.110 | 0.114    | 0.120 |

| E   | 2.10        | 2.37     | 2.64     | 0.082 | 0.093    | 0.104 |

| E1  | 1.20        | 1.30     | 1.40     | 0.047 | 0.051    | 0.055 |

| е   |             | 1.92 BSC | ;        |       | 0.075BSC | ;     |

| L   | 0.54 BSC    |          | 0.021BSC |       |          |       |

| θ   | 0°          |          | 8°       | 0°    |          | 8°    |

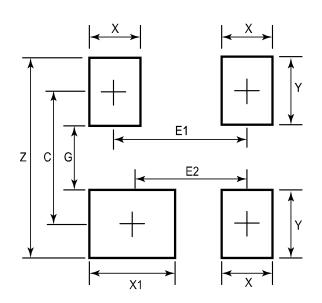

## Suggested Land Pattern

| SYM | DIMENSIONS  |        |  |  |

|-----|-------------|--------|--|--|

|     | MILLIMETERS | INCHES |  |  |

| С   | 2.20        | 0.087  |  |  |

| E1  | 1.92        | 0.076  |  |  |

| E2  | 1.72        | 0.068  |  |  |

| G   | 0.80        | 0.031  |  |  |

| Х   | 1.00        | 0.039  |  |  |

| X1  | 1.20        | 0.047  |  |  |

| Y   | 1.40        | 0.055  |  |  |

| Z   | 3.60        | 0.141  |  |  |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. **SUMSEMI** (and designs) are registered trademarks of SUM Semiconductor Corporation. Copyright SUM Semiconductor Corporation. All Rights Reserved.

All other trademarks mentioned are the property of their respective owners.