## Nano-Current Consumed Load Switch with Slew Rate Control

### DESCRIPTION

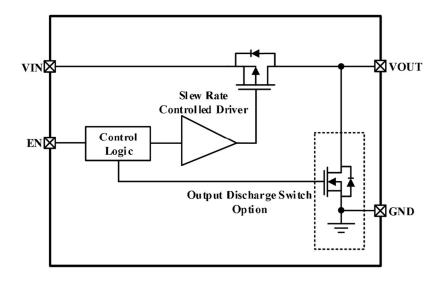

The SUM2572 is an ultra-efficiency, 2A rated, slew rate control Load Switch. It supports the lowest quiescent current ( $I_Q$ ) and shutdown current ( $I_{SD}$ ) in the industry. It helps designers to reduce leakage current, improve system efficiency, and increase battery lifetime.

The SUM2572 integrated slew rate control can also enhance system reliability by mitigating bus voltage swings during switching events. The slew rate control limits the inrush current for designs with heavy capacitive loads and thereby minimizing any resulting voltage droop at the power rails.

The SUM2572 Load Switch device supports a wide input voltage range and helps to improve operating life and system robustness. Furthermore, the device supports flexible applications and can be used in multiple voltage rail applications, which helps to reduce costs.

The SUM2572 Load Switch device is small utilizing a wafer level chip scale package with 4 bumps in a  $0.98 \text{ mm} \times 0.98 \text{ mm} \times 0.55 \text{ mm}$  die size and a 0.5 mm bump pitch.

### **FEATURES**

- Low R<sub>ON</sub> = 29 mΩ TYP. @ V<sub>IN</sub> = 5V, T<sub>A</sub> = 25°C

- Wide Input Range: 1.1 V to 5.5 V

- IOUT Max = 2 A

- Ultra-Low I<sub>Q</sub>: 6 nA Typ. @ V<sub>IN</sub> = 5V, T<sub>A</sub> = 25°C

- Controlled Rise Time: 340 μs @ V<sub>IN</sub> = 3.3V, T<sub>A</sub> = 25°C

- Internal EN Pull-Down Resistor

- Option for Integrated Output Discharge Switch

- Ultra-Small: 0.98 mm × 0.98 mm WLCSP

- RoHS and Green Compliant

### **APPLICATIONS**

- IoT

- Wearable electronics

- SSD

- Mobile Phones

- Low Power Subsystems

### **ORDER INFORMATION**

| Model   | Package | Ordering Number | Packing Option |

|---------|---------|-----------------|----------------|

| SUM2572 | WLCSP-4 | SUM2572CS4      | Tape and Reel  |

1

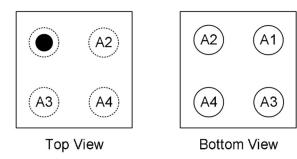

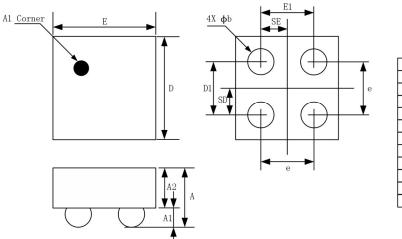

## **PIN CONFIGURATION (Top View)**

#### 0.98 mm × 0.98 mm WLSCP

### **PIN DESCRIPTIONS**

| Pin | Symbol | Description                         |

|-----|--------|-------------------------------------|

| A1  | Vout   | Switch Output                       |

| A2  | VIN    | Switch Input. Supply Voltage for IC |

| A3  | GND    | Ground                              |

| A4  | EN     | Enable to control the switch        |

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Description                                        | Value      | Units |

|----------------|----------------------------------------------------|------------|-------|

| Vin, Vout, Ven | Each Pin Voltage Range to GND                      | -0.3 to 6  | V     |

| lout           | Maximum Continuous Switch Current                  | 2          | А     |

| PD             | Maximum Power Dissipation at T <sub>A</sub> = 25°C | 1          | W     |

|                | Human Body Model, EIA/JESD22-a114                  | ±8         |       |

| ESD            | Charged Device Model, JS-002-2014                  | ±2         | kV    |

|                | Machine Model, EIA/JESD22-a115                     | ±300       | V     |

| T <sub>A</sub> | Operating Temperature Range                        | -40 to 85  | °C    |

| Tstg           | Storage Temperature                                | -65 to 150 | °C    |

| $J_A$          | Thermal Resistance, Junction to Ambient            | 110        | °C/W  |

NOTE:

Stresses beyond those listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### CAUTION

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SUMSEMI recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. SUMSEMI reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. Please contact SUMSEMI sales office to get the latest datasheet.

### **ELECTRICAL CHARACTERISTICS**

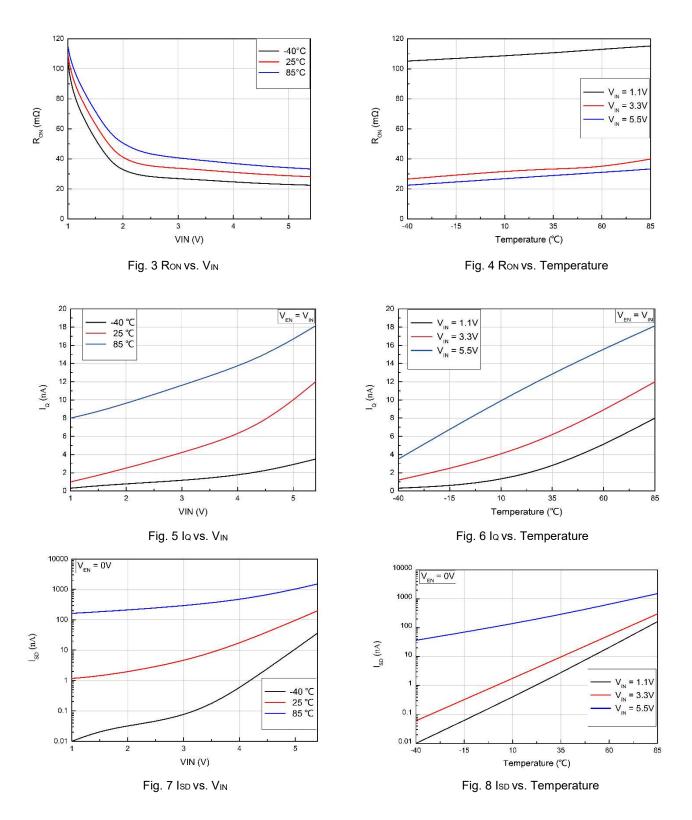

Unless otherwise noted;  $V_{IN}$  = 3.3 V,  $T_A$  = 25°C.

| Symbol           | Parameter                      | Conditions                                                                                   | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

|                  |                                | Basic Operation                                                                              |      |      |      |      |

| VIN              | Supply Voltage                 |                                                                                              | 1.1  |      | 5.5  | V    |

| lq               | Quiescent Current*1            | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = V <sub>EN</sub> = 5 V                             |      | 6    | 70   |      |

|                  |                                | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = V <sub>EN</sub> = 5 V, T <sub>A</sub> = 85°C      |      | 15   |      | nA   |

|                  | Shutdown Current               | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 1.1 V, V <sub>EN</sub> = 0 V                      |      | 1    |      | nA   |

|                  |                                | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 1.8 V, V <sub>EN</sub> = 0 V                      |      | 2    |      |      |

|                  |                                | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 3.3 V, V <sub>EN</sub> = 0 V                      |      | 6    | 50   |      |

| I <sub>SD</sub>  |                                | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 4.5 V, V <sub>EN</sub> = 0 V                      |      | 32   |      |      |

|                  |                                | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 5 V, V <sub>EN</sub> = 0 V                        |      | 70   |      |      |

|                  |                                | I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 5 V, V <sub>EN</sub> = 0 V, T <sub>A</sub> = 85°C |      | 860  |      |      |

|                  | On-Resistance                  | I <sub>OUT</sub> = 100 mA, V <sub>IN</sub> = V <sub>EN</sub> = 1.1 V                         |      | 110  |      | mΩ   |

|                  |                                | I <sub>OUT</sub> = 100 mA, V <sub>IN</sub> = V <sub>EN</sub> = 1.2 V                         |      | 88   |      |      |

|                  |                                | I <sub>OUT</sub> = 300 mA, V <sub>IN</sub> = V <sub>EN</sub> = 1.8 V                         |      | 50   |      |      |

| Ron              |                                | I <sub>OUT</sub> = 500 mA, V <sub>IN</sub> = V <sub>EN</sub> = 3.3 V                         |      | 33   | 46   |      |

|                  |                                | $I_{OUT} = 500 \text{ mA}, V_{IN} = V_{EN} = 3.3 \text{ V},$<br>$T_A = 85^{\circ}\text{C}$   |      | 39   |      |      |

|                  |                                | I <sub>OUT</sub> = 500 mA, V <sub>IN</sub> = V <sub>EN</sub> = 5V                            |      | 29   | 43   |      |

|                  |                                | $I_{OUT}$ = 500 mA, $V_{IN}$ = $V_{EN}$ = 5 V,<br>T <sub>A</sub> = 85°C                      |      | 35   |      |      |

| R <sub>DSC</sub> | Output Discharge<br>Resistance | V <sub>EN</sub> = 0 V, I <sub>FORCE</sub> = 10mA                                             | 70   | 85   | 100  | Ω    |

| Vін              | EN Input Logic High<br>Voltage | V <sub>IN</sub> = 1.1V - 1.8V                                                                | 0.9  |      |      | V    |

| VIH              |                                | V <sub>IN</sub> = 1.8V - 5.5V                                                                | 1.2  |      |      | V    |

| VIL              | EN Input Logic Low<br>Voltage  | V <sub>IN</sub> = 1.1V - 1.8V                                                                |      |      | 0.3  | V    |

| V IL             |                                | V <sub>IN</sub> = 1.8V - 5.5V                                                                |      |      | 0.4  | V    |

| $R_{EN}$         | EN pull resistance             | Internal Pull-Down Resistance                                                                | 7    | 10   | 13   | mΩ   |

| IEN              | EN Current                     | V <sub>EN</sub> = 5.5 V                                                                      |      | 0.56 | 0.8  | μA   |

\*1:  $I_Q$  of SUM2572 does not include the EN pin current through the pull-down or pull-up resistor  $R_{EN;}$

## **ELECTRICAL CHARACTERISTICS**

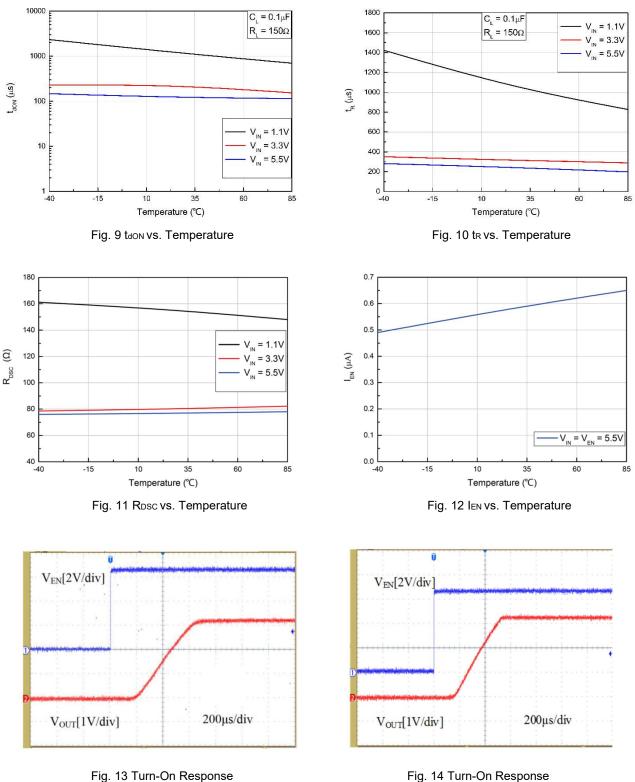

Unless otherwise noted;  $V_{IN}$  = 3.3 V,  $T_A$  = 25°C.

| Symbol            | Parameter                                  | Conditions                                      | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------------------|-------------------------------------------------|------|------|------|------|

| Switching         | g Characteristics                          |                                                 |      |      |      |      |

| t <sub>dON</sub>  | Turn-On Delay <sup>*2,4</sup>              | D 4500 0 0 4.5                                  |      | 222  |      | _    |

| t <sub>R</sub>    | V <sub>OUT</sub> Rise Time <sup>*2,4</sup> | R <sub>L</sub> = 150Ω, C <sub>OUT</sub> = 0.1μF |      | 340  |      |      |

| t <sub>dON</sub>  | Turn-On Delay <sup>*2,4</sup>              |                                                 |      | 211  |      |      |

| t <sub>R</sub>    | V <sub>OUT</sub> Rise Time <sup>*2,4</sup> | $R_L = 510\Omega, C_{OUT} = 0.1 \mu F$          |      | 378  |      |      |

| t <sub>dOFF</sub> | Turn-Off Delay* <sup>3,4</sup>             |                                                 |      | 0.52 |      | - µs |

| t⊧                | V <sub>OUT</sub> Fall Time <sup>*3,4</sup> | $R_L = 10\Omega, C_{OUT} = 0.1\mu F$            |      | 1.98 |      |      |

| t <sub>dOFF</sub> | Turn-Off Delay*3,4                         | R <sub>L</sub> = 510Ω, C <sub>OUT</sub> = 0.1μF |      | 1.22 |      |      |

| t⊦                | Vout Fall Time*3,4                         |                                                 |      | 16.5 |      |      |

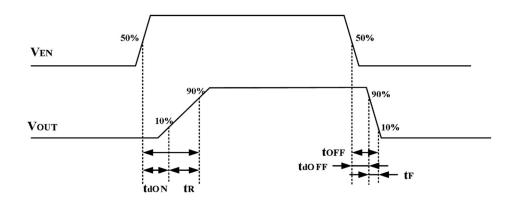

\*2:  $t_{ON} = t_{dON} + t_{R}$ ;

\*3: t<sub>OFF</sub> = t<sub>dOFF</sub> + t<sub>F</sub>;

\*4: By design; characterized, not production tested;

## SUM2572

### **ELECTRICAL PERFORMANCE**

## SUM2572

### **ELECTRICAL PERFORMANCE**

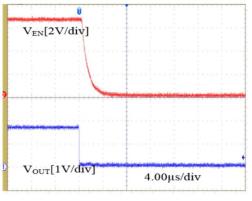

VIN=3.3V, CIN=1μF, Cout=0.1μF, RL=10Ω

Fig. 14 Turn-On Response VIN=3.3V, CIN=1µF, COUT=0.1µF, RL=510 $\Omega$

8

www.sumsemi.com.

### **ELECTRICAL PERFORMANCE**

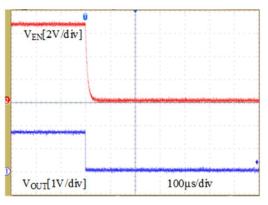

Fig. 15 Turn-Off Response  $V_{\text{IN}}{=}3.3V,\,C_{\text{IN}}{=}1\mu\text{F},\,C_{\text{OUT}}{=}0.1\mu\text{F},\,R_{\text{L}}{=}10\Omega$

Fig. 16 Turn-Off Response  $V{\rm IN}{=}3.3V,\,C{\rm IN}{=}1\mu F,\,C{\rm OUT}{=}0.1\mu F,\,R{\rm L}{=}510\Omega$

### **TIMING DIAGRAM**

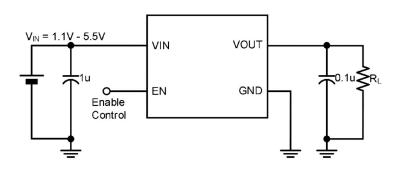

### **APPLICATION DESCRIPTION**

#### **Input Capacitor**

To limit the voltage drop on the input supply caused by transient inrush currents, an input bypass capacitor is recommended, which is recommended to be placed close to the  $V_{IN}$  pin. Higher value capacitors can further help to reduce the voltage drop.

### **Output Capacitor**

Depending on the sink current during system start-up and system turn-off, a capacitor must be placed on the output. A  $1.0\mu$ F or larger capacitor across V<sub>OUT</sub> and GND pins is recommended to accommodate load transient condition. This capacitor can also help to prevent parasitic inductance which can force the output voltage to fall below GND during turn-off. Undershoot can be caused by parasitic inductance from board traces or intentional load inductances. If load inductances do exist, use of an output capacitor can improve output voltage stability and system reliability. The C<sub>OUT</sub> capacitor should be placed close to the V<sub>OUT</sub> and GND pins.

#### **EN** Pin

The EN pin is compatible with active HIGH GPIO and CMOS logic voltage levels and operates over the 1.1V to 5.5V operating voltage range. Note that the SUM2572 incorporates an internal pull-down resistor on the enable pin, to ensure that the device remains OFF, in the event that the pin is left floating.

### **Output Discharge Function**

The SUM2572(With output discharge) has an internal discharge N-channel FET switch on the  $V_{OUT}$  pin. When EN signal turns the main power FET to an off state, the N-channel switch turns on to discharge an output capacitor quickly.

#### **Board Layout**

For the best performance, all traces should be as short as possible to minimize the inductance and parasitic effects. The input and output capacitors should be kept as close as possible to the input and output pins respectively. Using wide traces for input, output, and GND help reducing the case to ambient thermal impedance.

### **APPLICATION CIRCUITS**

### **PACKAGE OUTLINE**

#### WLCSP-4

#### 0.98mm X 0.98mm WLCSP Package Outline Diagram

COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER) SYMBOL MIN NOM MAX А 0.500 0.5500.600 0.225 A1 0.250 0.275 0.275 A2 0.300 0.325 0.990 0.965 0.980 D Е 0.965 0.980 0.990 D1 0.450 0.500 0.550 E1 0.4500.500 0.550b 0.266 0.316 0.366 0.500 BSC е SD 0.250 BSC SE 0.250 BSC