# **High Input Ultra-high PSRR 300mA LDO**

## **DESCRIPTION**

SUM3565 is a high input voltage and ultra high PSRR 300 mA LDO with enable function that output adjustable from  $1.0 \text{ V} \sim 5 \text{ V}$ , is designed specifically for portable battery-powered applications which require low quiescent current. The consumption of type 50 uA ensures long battery life and dynamic transient boost feature improves device transient response for wireless communication applications.

SUM3565 is offered SOT23-5 package.

## **FEATURES**

- Wide input voltage range from 3 V to 24 V

- Up to 300 mA Load Current

- I<sub>Q</sub> is 50 μA typical

- ADJ Output Voltage range 1.0 V ~ 5.0 V

- Very Low dropout is 330 mV at 150 mA Load @ V<sub>OUT</sub> = 3.3V

- Excellent load/line transient response

- Ultra High Ripple Rejection: 90 dB at 1 KHz

- Package is SOT23-5

## ORDER INFORMATION

| Model       | Package | Ordering Number | Packing Option      |

|-------------|---------|-----------------|---------------------|

| SUM3565-ADJ | SOT23-5 | SUM3565-ADJKA5  | Tape and Reel, 3000 |

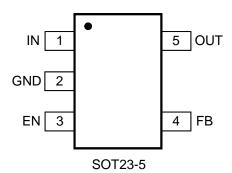

# **PIN CONFIGURATION (Top View)**

# **PIN DESCRIPTIONS**

| Pin | Symbol | Description                        |

|-----|--------|------------------------------------|

| 1   | IN     | Supply input pin.                  |

| 2   | GND    | Ground.                            |

| 3   | EN     | Enable control input, active high. |

| 4   | FB     | Set the output voltage.            |

| 5   | OUT    | Output pin.                        |

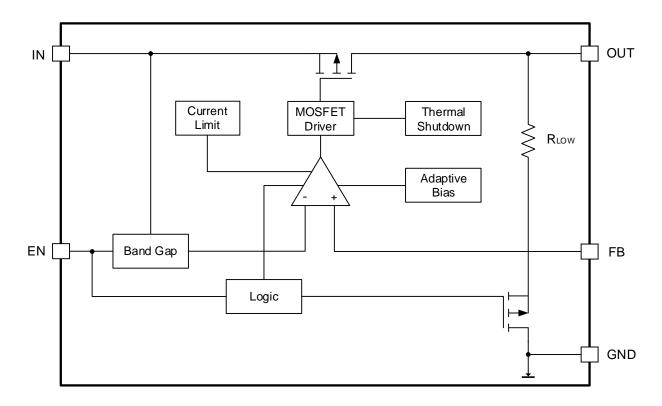

# **BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTION**

#### INPUT CAPACITOR

A 1 µF ~ 10 µF ceramic capacitor is recommended to connect between IN and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. This input capacitor must be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both IN and GND.

### **OUTPUT CAPACITOR**

An output capacitor is required for the stability of the LDO. The recommended output capacitance is from 1 µF to 10  $\mu$ F, Equivalent Series Resistance (ESR) is from 5 m $\Omega$  to 100 m $\Omega$ , and temperature characteristics are X7R or X5R. Higher capacitance values help to improve load/line transient response. The output capacitance may be increased to keep low undershoot/overshoot. Place output capacitor as close as possible to OUT and GND pins.

#### **ENABLE**

The SUM3565 delivers the output power when it is set to enable state. When it works in disable state, there is no output power and the operation quiescent current is almost zero. The enable pin (EN) is active high.

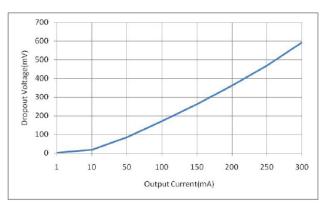

### **DROPUT VOLTAGE**

The SUM3565 uses a PMOS pass transistor to achieve low dropout. When (VIN - VOUT) is less than the dropout voltage (V<sub>DO</sub>), the PMOS pass device is in the linear region of operation and the input-to-output resistance is the R<sub>DS(ON)</sub> of the PMOS pass element. V<sub>DO</sub> scales approximately with output current because the PMOS device behaves like a resistor in dropout mode. As with any linear regulator, PSRR and transient response degrade as (V<sub>IN</sub> - V<sub>OUT</sub>) approaches dropout operation.

## THERMAL SHUTDOWN

Thermal shutdown protection disables the output when the junction temperature rises to approximately 155°C. Disabling the device eliminates the power dissipated by the device, allowing the device to cool. When the junction temperature cools to approximately 130°C, the output circuitry is again enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits regulator dissipation, protecting the LDO from damage as a result of overheating. Activating the thermal shutdown feature usually indicates excessive power dissipation as a result of the product of the (V<sub>IN</sub> - V<sub>OUT</sub>) voltage and the load current. For reliable operation, limit junction temperature to 125°C maximum.

### THERMAL CONSIDERATIONS

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications the maximum junction temperature is 125°C and  $T_A$  is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOT23-5 package, the thermal resistance,  $\theta_{JA}$ , is 250°C/W on the test board. The maximum power dissipation at

$T_A = 25$ °C can be calculated by the following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (250^{\circ}C/W) = 0.4 \text{ W for SOT23-5 package}$$

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ .

#### **CURRENT-LIMIT PROTECTION**

The SUM3565 provides current limit function to prevent the device from damages during over-load or shorted-circuit condition. This current is detected by an internal sensing transistor.

## **Layout Guidelines**

- Place input and output capacitors as close to the device as possible.

- Use copper planes for device connections in order to optimize thermal performance.

- Place thermal vias around the device to distribute heat.

- Do not place a thermal via directly beneath the thermal pad of the DRV package. A via can wick solder or solder paste away from the thermal pad joint during the soldering process, leading to a compromised solder joint on the thermal pad.

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                                                    | Value   | Unit       |      |

|---------------------|--------------------------------------------------------------|---------|------------|------|

| V <sub>IN</sub>     | Input Voltage <sup>(1)</sup>                                 |         | -0.3 to 30 | V    |

| V <sub>OUT</sub>    | Output Voltage                                               |         | -0.3 to 6  | V    |

| $V_{EN}$            | Chip Enable Input                                            |         | -0.3 to 30 | V    |

| T <sub>J(MAX)</sub> | Maximum Junction Temperature                                 |         | 150        | °C   |

| T <sub>STG</sub>    | Storage Temperature                                          |         | -65 to 150 | °C   |

| ESD (HBM)           | Human Body Model <sup>(2)</sup>                              |         | 2000       | V    |

| ESD (CDM)           | ESD Capability <sup>(2)</sup>                                |         | 1500       | V    |

| Latch up            | Current Maximum Rating <sup>(2)</sup>                        |         | 200        | mA   |

| Reja                | Thermal Characteristics, Thermal Resistance, Junction-to-Air | SOT23-5 | 250        | °C/W |

#### NOTES:

Stresses beyond those listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 1. Refer to Electrical Characteristics and Application Information for Safe Operating Area.

- 2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per EIA/JESD22-A114;

CDM tested per JESD22-C101;

Latch up Current Maximum Rating tested per JEDEC78.

# **CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. SUMSEMI recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications. SUMSEMI reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. Please contact SUMSEMI sales office to get the latest datasheet.

### RECOMMENDED OPERATING CONDITIONS

| Symbol           | Item                                                    | Rating     | Unit |

|------------------|---------------------------------------------------------|------------|------|

| V <sub>IN</sub>  | Input Voltage                                           | 3 to 24    | V    |

| l <sub>out</sub> | Output Current                                          | 0 to 300   | mA   |

| TA               | Operating Ambient Temperature                           | - 40 to 85 | °C   |

| CIN              | Effective Input Ceramic Capacitor Value                 | 1 to 10    | μF   |

| Соит             | Effective Output Ceramic Capacitor Value                | 1 to 10    | μF   |

| ESR              | Input and Output Capacitor Equivalent Series Resistance | 5 to 100   | mΩ   |

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{OUT} + 2V; I_{OUT} = 10 \text{mA}, C_{IN} = C_{OUT} = 2.2 \mu F, unless otherwise noted. Typical values are at T<sub>A</sub> = +25 °C.) (3)$

| Symbol              | Parameter                | Test Conditions                                                     | Min.  | Тур.  | Max.   | Unit              |

|---------------------|--------------------------|---------------------------------------------------------------------|-------|-------|--------|-------------------|

| V <sub>IN</sub>     | Operating Input Voltage  |                                                                     | 3     |       | 24     | V                 |

| V <sub>FB</sub>     | FB Voltage               | T <sub>A</sub> = +25°C                                              | 0.591 | 0.600 | 0.609  | V                 |

|                     |                          | -40°C ≤ T <sub>A</sub> ≤ 85°C                                       | 0.588 |       | 0.612  |                   |

| Line <sub>REG</sub> | Line Regulation          | $V_{OUT} + 2 \le V_{IN} \le 24 \text{ V},$                          | 0.05  | 0.00  | 0/ /\/ |                   |

|                     |                          | Іоит = 10 mA                                                        |       | 0.05  | 0.20   | %/V               |

| $V_{DROP}$          | DropoutVoltage           | Іоит = 300 mA, V <sub>оит</sub> = 3.3 V                             |       | 600   | 950    | mV                |

| V DROP              | Dropout Voltage          | Іоит = 150 mA, V <sub>оит</sub> = 3.3 V                             |       | 270   | 450    | mV                |

|                     |                          | 1 mA ≤ I <sub>ОUТ</sub> ≤ 300 mA,                                   |       |       |        |                   |

| Load <sub>REG</sub> | Load Regulation          | $V_{IN} = V_{OUT} + 2 V$                                            |       |       | 40     | mV                |

|                     |                          | T <sub>A</sub> = + 25°C                                             |       |       |        |                   |

| I <sub>LMT</sub>    | Current Limit            | V <sub>IN</sub> = V <sub>OUT</sub> + 2 V                            | 300   | 500   |        | mA                |

| I <sub>SHORT</sub>  | Short Current Limit      | V <sub>IN</sub> = V <sub>OUT</sub> + 2 V                            |       | 100   |        |                   |

| ΙQ                  | Quiescent Current        | Іоит = 0 mA                                                         |       | 50    | 80     | μA                |

| I <sub>Q_OFF</sub>  | Standby Current          | V <sub>EN</sub> = 0 V, T <sub>A</sub> = 25°C                        |       | 0.1   | 1      | μA                |

| VENH                | EN Pin Threshold Voltage | EN Input Voltage "H"                                                | 1.0   |       |        | V                 |

| VENL                | EN Pin Threshold Voltage | EN Input Voltage "L"                                                |       |       | 0.4    | V                 |

| I <sub>EN</sub>     | EN Pin Current           | V <sub>EN</sub> = 0 to 24 V                                         |       | 1     |        | μA                |

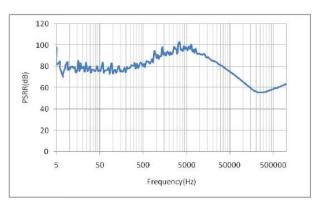

| DODD                | Power Supply Rejection   | V <sub>IN</sub> = V <sub>OUT</sub> + 2 V, I <sub>OUT</sub> = 20 mA, |       | 00    |        | ID.               |

| PSRR                | Ratio                    | f = 1 kHz                                                           |       | 90    |        | dB                |

|                     |                          | $V_{IN} = V_{OUT} + 2 V$ , $I_{OUT} = 1 mA$ ,                       |       |       |        |                   |

| en                  | Output Noise Voltage     | f = 10 Hz to 100 kHz,                                               |       | 70    |        | μV <sub>RMS</sub> |

|                     |                          | Vout = 3.3 V, Cout = 1 $\mu$ F <sup>(5)</sup>                       |       |       |        |                   |

| R <sub>dis</sub>    | Output discharge FET     | V <sub>EN</sub> < V <sub>IL</sub> (output disable)                  |       | 100   |        | Ω                 |

| Ndis                | RDSON                    | VEN < VII. (Output disable)                                         |       | 100   |        | 12                |

| T <sub>SD</sub>     | Thermal Shutdown         | Temperature Increasing from                                         |       | 155   |        | °C                |

| I SD                | Temperature              | $T_A = +25^{\circ}C^{(5)}$                                          |       | 133   |        |                   |

| T <sub>SDH</sub>    | Thermal Shutdown         | Temperature Falling from TSD <sup>(5)</sup>                         |       | 25    | , Τ    | °C                |

| I 2DH               | Hysteresis               | Temperature Failing from 13De                                       |       | 25    |        |                   |

#### NOTES:

- 3. Here  $V_{IN}$  means internal circuit can work normal. If  $V_{IN} < V_{OUT}$ , Output voltage follow  $V_{IN}$  (I<sub>OUT</sub> = 1 mA), circuit is safety.

- 4. V<sub>DROP</sub> FT test method: test the V<sub>OUT</sub> voltage at V<sub>SET</sub> + V<sub>DROPMAX</sub> with 300 mA output current.

- 5. Guaranteed by design and characterization. not a FT item.

- 6. The minimum operating voltage is 3 V.  $V_{DROP} = V_{IN(MIN)} V_{OUT}$ .

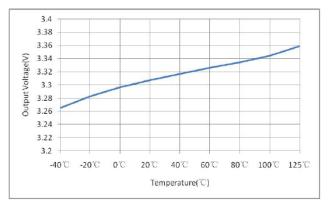

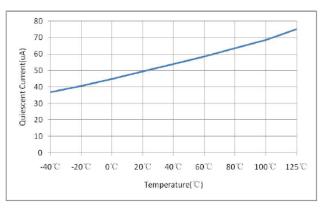

# **TYPICAL CHARACTERISTICS**

Voltage set 3.3 V (V<sub>IN</sub> = V<sub>OUT</sub> + 2 V, I<sub>OUT</sub> = 10 mA, R1 = 200 k $\Omega$ , R2 = 200 k $\Omega$ , C<sub>IN</sub> = C<sub>OUT</sub> = 1.0  $\mu$ F, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C).

Output Voltage vs. Temperature

Quiescent Current vs. Temperature

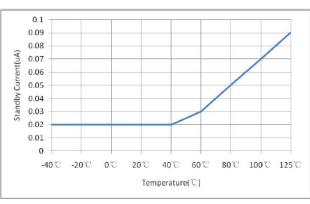

Standby Current vs. Temperature

Dropout Voltage vs Output Current

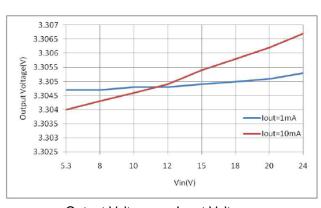

Output Voltage vs. Input Voltage

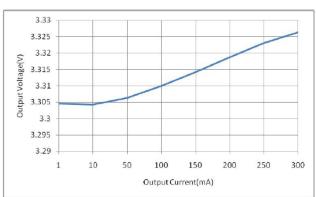

Output Voltage vs. Output Current

# **TYPICAL CHARACTERISTICS (Continued)**

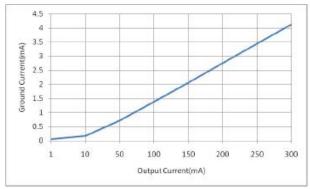

Ground Current vs. Output Current

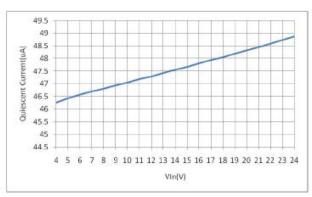

Quiescent Current vs. Input Voltage

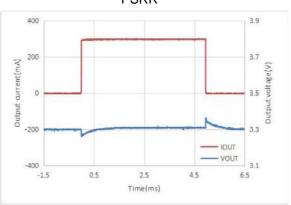

**PSRR**

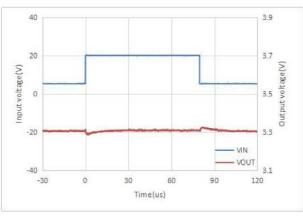

Line-Transient Response(Iout = 20 mA)

Load-Transient Response

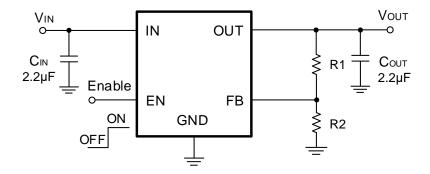

# **APPLICATION CIRCUITS**

## NOTE:

- 1.  $V_{OUT} = 0.6 V * (R1 + R2) / R2$

- 2. Recommended R2 = 100 K ~ 1 M

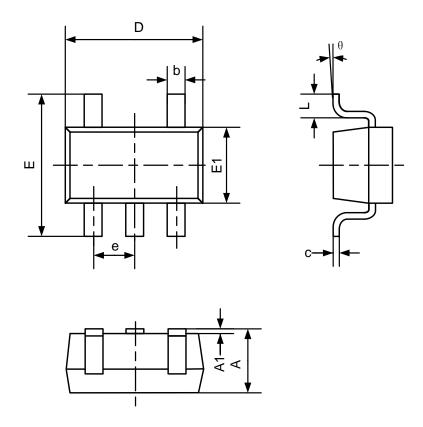

# **PACKAGE OUTLINE**

# SOT23-5

| Comphal | Dimensions In Millimeters |       |  |

|---------|---------------------------|-------|--|

| Symbol  | Min                       | Max   |  |

| A       | 1.050                     | 1.250 |  |

| A1      | 0.000                     | 0.100 |  |

| b       | 0.350                     | 0.500 |  |

| С       | 0.100                     | 0.200 |  |

| D       | 2.820                     | 3.020 |  |

| Е       | 2.650                     | 3.050 |  |

| E1      | 1.500                     | 1.700 |  |

| е       | 0.950BSC                  |       |  |

| L       | 0.300                     | 0.600 |  |

| θ       | 0°                        | 8°    |  |